MIPS32_Single_Cycle_Processor

所属分类:嵌入式/单片机/硬件编程

开发工具:Verilog

文件大小:0KB

下载次数:0

上传日期:2019-02-16 11:34:35

上 传 者:

sh-1993

说明: MIPS-32单周期处理器,具有R型指令。通过Verilog.编程。,

(MIPS -32 single cycle processor with R type instruction. Programmed via Verilog.,)

文件列表:

ALU32_testbench.v (3500, 2019-02-16)

ALU_32.v (4883, 2019-02-16)

AND_32.v (1540, 2019-02-16)

FULL_ADDER.v (387, 2019-02-16)

FULL_ADDER1_testbench.v (586, 2019-02-16)

FULL_ADDER_32.v (2854, 2019-02-16)

FULL_ADDER_testbench.v (892, 2019-02-16)

HALF_ADDER.v (185, 2019-02-16)

LEFT_SHIFTER.v (11545, 2019-02-16)

LEFT_SHIFTER_testbench.v (823, 2019-02-16)

MUX_2.v (331, 2019-02-16)

MUX_2_testbench.v (395, 2019-02-16)

MUX_4.v (313, 2019-02-16)

MUX_4_testbench.v (713, 2019-02-16)

MUX_8.v (409, 2019-02-16)

MUX_8_testbench.v (1673, 2019-02-16)

NOR_32.v (1539, 2019-02-16)

OR_32.v (1472, 2019-02-16)

RIGHT_SHIFTER_ARITHMETIC.v (11584, 2019-02-16)

RIGHT_SHIFTER_ARITHMETIC_testbench.v (640, 2019-02-16)

SUBSTRACTOR_32.v (1573, 2019-02-16)

SUBSTRACTOR_32_testbenchv.v (643, 2019-02-16)

XOR_32.v (1537, 2019-02-16)

concat.v (1171, 2019-02-16)

concat_for_sltu.v (1102, 2019-02-16)

concat_for_sltu_testbench.v (301, 2019-02-16)

concat_testbench.v (292, 2019-02-16)

control_unit.v (873, 2019-02-16)

mips32.v (10430, 2019-02-16)

mips32_testbench.v (901, 2019-02-16)

mips32_testbench.v.bak (1122, 2019-02-16)

mips_register_testbench.v (646, 2019-02-16)

mips_registers.v (550, 2019-02-16)

# MIPS32_Single_Cycle_Processor

This project include a single cycle MIPS processor but only supporting the R-type instructions in

the MIPS Green Sheet.

This Processor takes a 32 bit instruction as input and write the result to the $rd register as R-type instructions require.

Only the register block desingned using by behavioral but other than that, all block designed using by structural.

## --> General Design For Processor

This schema includes general processor design for this project. All implementations are made according to the blocks in

this schema like register block, control unit, alu unit block etc.

## --> Desing For Control Unit

Control unit must takes 6 bits input and gives 3 bits outputs. This schema shows the design of 3 bits that will be output.

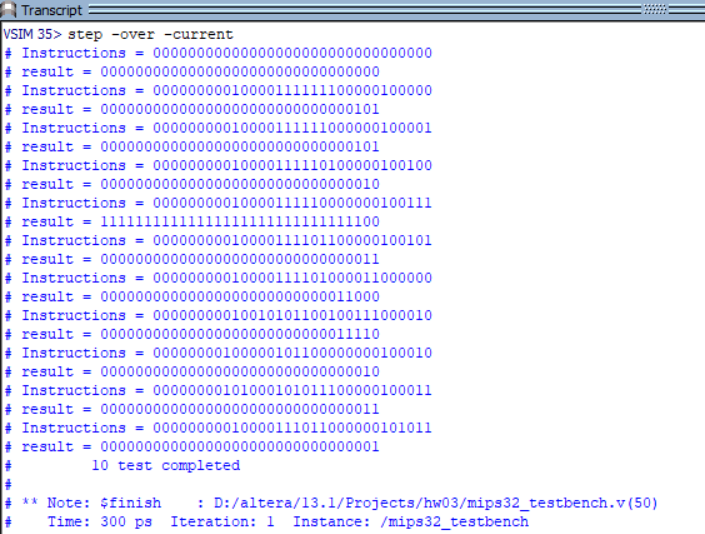

## --> Modelsim Result

## --> Register File Result

Register file result is related to test instructions. The test instructions are given within the modelim results.

近期下载者:

相关文件:

收藏者: